## 香港中文大學

The Chinese University of Hong Kong

CENG3430 Rapid Prototyping of Digital Systems

# Lecture 03: Architectural Styles of VHDL

## Recall: What we have done in Lab01

#### Hardware

end AND arch;

#### Simulation

```

architecture Behavioral of AND TEST is

component AND Gate

port(A, B: in STD LOGIC;

C: out STD LOGIC);

end component;

signal ai, bi: STD LOGIC;

signal ci: STD LOGIC;

begin

AND Gate port map (A => ai, B => bi,

C \Rightarrow ci);

process

begin

ai <= '0'; bi <= '0';

wait for 100 ns;

ai <= '1'; bi <= '0';

wait for 100 ns;

ai <= '0'; bi <= '1';

wait for 100 ns;

ai <= '1'; bi <= '1';

wait;

end process;

```

## **Outline**

- Architectural Design Methods

- Data Flow Design (concurrent statements)

- Structural Design ("port map")

- Behavioral Design ("process")

- Concurrent vs. Sequential Statements

- Design Constructions

- Concurrent: when-else, with-select-when

- Sequential: if-then-else, case-when, loop

## **Data Flow: Use Concurrent Statements**

- Data flow design method uses concurrent statements instead of sequential statements.

- Concurrent statements can be interchanged freely.

- There's no "execution order" for concurrent statements.

```

1 library IEEE; %Vivado2014.4 tested ok

2 use IEEE.STD LOGIC 1164.ALL;

3 entity eqb comp4 is

port (a, b: in std logic vector(3 downto 0);

equals, bigger: out std logic);

5

end eqb comp4;

7 architecture dataflow4 of eqb comp4 is

begin

equals <= '1' when (a = b) else '0'; --concurrent

10 bigger <= '1' when (a > b) else '0'; --concurrent

```

Lines 9 & 10 will be executed whenever signal a or b (or both) changes.

Student ID: \_\_\_\_\_ Date: Name:

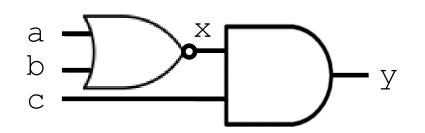

Draw the schematic circuit of this code:

```

1 library IEEE; --Vivado 14.4

2 use IEEE.STD LOGIC 1164.ALL;

entity abc is

port (a,b,c: in std logic;

5

y: out std logic);

end abc;

7 architecture abc arch of abc is

signal x : std logic;

begin

10 x \le a \text{ nor } b;

11 y \le x and c;

12 end abc arch;

```

Answer:

## **Outline**

- Architectural Design Methods

- Data Flow Design (concurrent statements)

- Structural Design ("port map")

- Behavioral Design ("process")

- Concurrent vs. Sequential Statements

- Design Constructions

- Concurrent: when-else, with-select-when

- Sequential: if-then-else, case-when, loop

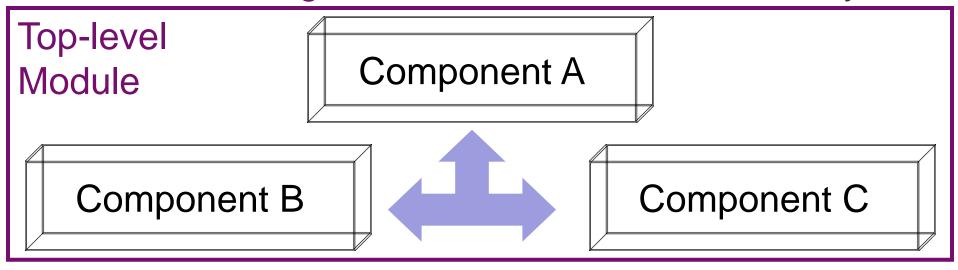

# Structural Design: Use "port map"

Structural Design: Like a circuit but describe it by text.

Connected by **port map** in the architecture body of the top-level design module

Design Steps:

Step 1: Create entities

Step 2: Create components from entities

Step 3: Use "port map" to relate the components

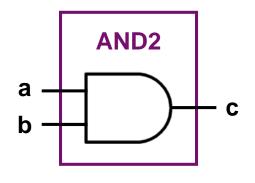

# **Step 1: Create Entities**

```

1 library IEEE;

2 use IEEE.STD LOGIC 1164.ALL;

3 entity and2 is

4 port (a,b: in STD LOGIC;

c: out STD LOGIC );

6 end and2;

7 architecture and2 arch of and2 is

8 begin

c \le a \text{ and } b;

10 end and2 arch;

12 library IEEE;

13 use IEEE.STD LOGIC 1164.ALL;

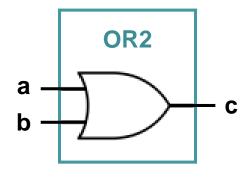

14 entity or2 is

15 port (a,b: in STD LOGIC;

c: out STD LOGIC );

16

17 end or2;

18 architecture or 2 arch of or 2 is

19 begin

20 c \leq a \text{ or } b;

21 end or2 arch;

CENG3430 Lec03: Architectural Styles of VHDL

```

# **Step 2: Create Components**

```

component and2 --create components--

port (a,b: in std logic; c: out std logic);

end component;

component or2 --create components--

port (a,b: in std logic; c: out std logic);

end component;

signal con1 signal: std logic; --internal signal--

(optional)

AND2

OR<sub>2</sub>

```

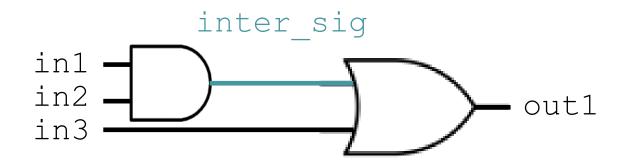

# **Step 3: Connect Components**

#### label1 & label 2 are line labels

Lines can be interchanged for the same circuit design.

# Put Together: A Running Example

```

1 library IEEE;

1 library IEEE;

Top-level Module

2 use IEEE.STD LOGIC 1164.ALL;

2 use IEEE.STD LOGIC 1164.ALL;

3 entity and2 is

Step 1

4 port (a,b: in STD LOGIC;

4 entity test is

c: out STD LOGIC );

5 port (in1: in STD LOGIC; in2: in STD LOGIC;

in3: in STD LOGIC;

6 end and2;

7 architecture and2 arch of and2 is

7 out1: out STD LOGIC );

8 begin

8 end test;

c \le a and b;

9 architecture test arch of test is

10 end and2 arch;

10 component and2 --create component

Step 2

port (a,b: in std logic; c: out std logic);

12 library IEEE;

12 end component;

13 use IEEE.STD LOGIC 1164.ALL;

13 component or2 --create component

14 entity or2 is

port (a,b: in std logic; c: out std logic);

Step 1

15 end component;

15 port (a,b: in STD LOGIC;

c: out STD LOGIC);

16 signal inter sig: std logic;

Step 3

17 end or2;

17 begin

18 label1: and2 port map (in1, in2, inter sig);

18 architecture or 2 arch of or 2 is

19 begin

19 label2: or2 port map (inter sig, in3, out1);

20 end test arch;

20 c <= a or b;

inter sig

in1 -

21 end or2 arch;

out1

CENG3430 Lec03: Architectural Styles of VHDL

```

Student ID: \_\_\_\_\_ Date: Name: \_\_\_\_

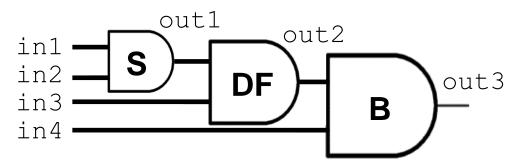

Draw the schematic diagram for the following lines:

- When will lines i and ii be executed?

Answer:

- Complete lines i and ii if the circuit is as follows:

```

i label_u0:

ii label_u1:

a

b

c

```

# **Another Running Example**

```

entity test andand2 is

inter sig

port (in1: in STD LOGIC;

in1

in2: in STD LOGIC;

in2

out1

in3

in3: in STD LOGIC;

out1: out STD LOGIC

);

end test andand2;

architecture test and and 2 arch of test and and 2 is

component and2

No need to create the

component for the same

port (a, b: in std_logic; c: out std_logic);

entity for several times

end component ;

signal inter sig: std logic;

begin

But you can use

label1: and2 port map (in1, in2, inter sig);

the component

label2: and2 port map (inter sig, in3, out1);

multiple times

```

end test andand2 arch;

| Student ID: | Date: |

|-------------|-------|

| Name:       |       |

Draw the schematic diagram and fill in the truth table for the following the half-adder:

```

library IEEE; --Vivado 14.4 ok

use IEEE.STD LOGIC 1164.ALL;

entity half adder is -- another example

port ( x: in bit; y: in bit;

sum: out bit; carry: out bit );

end half adder;

architecture arch of half adder is

component xor2

port(a,b: in bit; c: out bit);

end component;

component and2

port(a,b: in bit; c: out bit);

end component;

begin

label1: xor2 port map (x, y, sum);

label2: and2 port map (x, y, carry);

end arch;

```

CENG3430 Lec03: Architectural Styles of VHDL

| ζ | sum   |

|---|-------|

| 7 | carry |

|   | l     |

| input |   | output |     |

|-------|---|--------|-----|

| x     | У | carry  | sum |

|       |   |        |     |

|       |   |        |     |

|       |   |        |     |

|       |   |        |     |

## Structural vs. Data Flow

#### **Structural**

#### (port map)

```

architecture test arch of test is

component and2

port (a,b: in std logic;

c: out std logic);

end component;

component nor2

port (a,b: in std logic;

c: out std logic);

end component;

signal x: std logic;

begin

label1: nor2 port map (a, b, x);

label2: and2 port map (x, c, y);

end test arch;

```

#### **Data Flow**

#### (concurrent statements)

```

architecture test_arch of test is

signal x : std_logic;

begin

x <= a nor b;

y <= x and c;

end test_arch;</pre>

```

## **Outline**

- Architectural Design Methods

- Data Flow Design (concurrent statements)

- Structural Design ("port map")

- Behavioral Design ("process")

- Concurrent vs. Sequential Statements

- Design Constructions

- Concurrent: when-else, with-select-when

- Sequential: if-then-else, case-when, loop

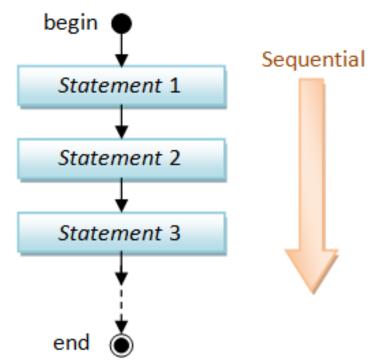

# Behavioral Design: Use "process"

- Behavioral design is sequential

- Just like a sequential program

- The keyword is "process":

- The main character is "process (sensitivity list)".

- A process is executed when one (or more) of the signals in the sensitivity list changes.

- Statements inside a process are sequentially executed.

# **Behavioral Design Example**

```

library IEEE; --vivado14.4

use IEEE.STD LOGIC 1164.ALL;

entity eqcomp4 is port(

port (a, b: in std logic; vector(3 downto 0)

equals: out std logic);

end eqcomp4;

architecture behavioral of egcomp4 is

begin

begin

if a = b then

equals <= '1';

Sequential Execution:

Statements inside a process are

else

equals <= '0';

sequentially executed.

end if;

end process;

end behavioral;

```

## Recall: What we have done in Lab01

#### Hardware

- It is legal to have a process WITHOUT a sensitivity list.

- Such process MUST have some kind of time-delay or wait (Lec05).

#### **Simulation**

```

architecture Behavioral of AND TEST is

component AND Gate

port (A, B: in STD LOGIC;

C: out STD LOGIC);

end component;

signal ai, bi: STD LOGIC;

signal ci: STD LOGIC;

begin

AND Gate port map (A => ai, B => bi,

C \Rightarrow ci);

process

begin

ai <= '0'; bi <= '0';

wait for 100 ns;

ai <= '1'; bi <= '0';

wait for 100 ns;

ai <= '0'; bi <= '1';

wait for 100 ns;

ai <= '1'; bi <= '1';

wait:

end process;

```

end Behavioral;

## **Outline**

- Architectural Design Methods

- Data Flow Design (concurrent statements)

- Structural Design ("port map")

- Behavioral Design ("process")

- Concurrent vs. Sequential Statements

- Design Constructions

- Concurrent: when-else, with-select-when

- Sequential: if-then-else, case-when, loop

# Concurrent vs. Sequential Statements

#### Concurrent Statement

- Statements inside the architecture body can be executed concurrently, except statements enclosed by a process.

- Every statement will be <u>executed once</u> whenever <u>any</u> signal in the statement changes.

#### Sequential Statement

- Statements within a process are executed sequentially,

and the result is obtained when the process is complete.

- process (sensitivity list): When one or more signals in the sensitivity list change state, the process executes once.

- A process can be treated as one concurrent statement in the architecture body.

# **Concurrent with Sequential**

```

1 library IEEE; --vivado14.4 ok

out1

in1

out2

2 use IEEE.STD LOGIC 1164.ALL;

in2.

in3

3 entity conc ex is

4 port (in1, in2, in3: in std logic;

5

out1, out2 : inout std logic);

6 end conc ex;

7 architecture for ex arch of conc ex is

8 begin

9 process (in1, in2)

The process (9-12) and

10 begin

line 13 are concurrent

11  out1 <= in1 and in2;</pre>

and can be interchanged!

12 end process;

13 out2 <= out1 and in3; -- concurrent statement

14 end for ex arch;

```

Student ID: \_\_\_\_\_ Date: Name: \_\_\_\_

State concurrent and sequential statements:

```

1 architecture for ex arch of for ex is

2 begin

3

outx1 < = out1 and in3;

process (in1, in2)

begin

5

out1 <= in1 and in2;

6

end process;

8

outx2 < = out1 or in3;

9 end for ex arch;

```

Student ID: \_\_\_\_\_ Date: Name: \_\_\_\_

Use structural, data flow, and behavioral designs to implement the following circuit in VHDL:

## **Outline**

- Architectural Design Methods

- Data Flow Design (concurrent statements)

- Structural Design ("port map")

- Behavioral Design ("process")

- Concurrent vs. Sequential Statements

- Design Constructions

- Concurrent: when-else, with-select-when

- Sequential: if-then-else, case-when, loop

CENG3430 Lec03: Architectural Styles of VHDL

# **Design Constructions**

- Concurrent: Statements that can be stand-alone

- 1) when-else

2) with-select-when

Concurrent: **OUTSIDE** process

- Sequential: Statements inside the process

- 1) if-then-else

- 2) case-when

Sequential – **INSIDE** process

3) for-in-to-loop

# Concurrent 1) when-else

```

in1 ____ out1

```

```

1 library IEEE;

2 use IEEE.STD LOGIC 1164.ALL;

3 entity when ex is

4 port (in1, in2 : in std logic;

out1 : out std logic);

6 end when ex;

7 architecture when ex arch of when ex is

Condition based

8 begin

out1 <= '1' when in1 = '1' and in2 = '1' else '0';

10 end when ex arch;

when condition is true then out1 <= '1'

otherwise then out1 <= '0'

```

Student ID: \_\_\_\_\_ Date: Name: \_\_\_\_

• Fill in line 9 using when-else:

```

1 library IEEE;

2 use IEEE.STD LOGIC 1164.ALL;

3 entity when ex is

4 port (in1, in2: in std logic;

out1 : out std logic);

6 end when ex;

7 architecture when ex arch of when ex is

8 begin

9

```

10 end when ex\_arch; CENG3430 Lec03: Architectural Styles of VHDL

Student ID: \_\_\_\_\_ Date: Name: \_\_\_\_

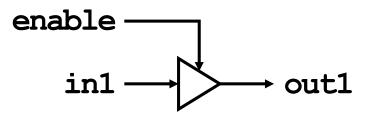

Fill in the empty line to realize tri-state logic:

- 1 library IEEE;

- 2 use IEEE.STD\_LOGIC\_1164.ALL;

- 3 entity tri ex is

- 4 port (in1, enable: in std logic;

- 5 ut1: out std logic);

- 6 end tri ex;

- 7 architecture tri\_ex\_arch of tri\_ex is

- 8 begin

9

11 end tri ex arch;

| in1 | enable | out1 |

|-----|--------|------|

| 0   | 0      | Z    |

| 1   | 0      | Z    |

| 0   | 1      | 0    |

| 1   | 1      | 1    |

# Concurrent 2) with-select-when

```

in1

out1

1 library IEEE;

2 use IEEE.STD LOGIC 1164.ALL;

3 entity when ex is

4 port (in1, in2 : in std logic;

out1 : out std logic);

6 end when ex;

7 architecture when ex arch of when ex is

begin

with in1 select Signal based

out1 <= in2 when '1', ← when in1='1' then out1 <= in2

10

'0' when others; ← when in1 = other cases

11

then out1 <= '0'

12 end when ex arch;

```

Student ID: \_\_\_\_\_ Date: Name: \_\_\_\_

• Fill in lines 9~11 using with-select-when:

```

1 library IEEE;

in1

2 use IEEE.STD LOGIC 1164.ALL;

3 entity when ex is

4 port (in1, in2 : in std logic;

out1 : out std logic);

6 end when ex;

7 architecture when ex arch of when ex is

8 begin

10

11

```

CENG3430 Lec03: Architectural Styles of VHDL

12 end when ex arch;

#### when-else VS. with-select-when

Concurrent 1) when-else: Condition based

out1 <= '1' when in1 = '1' and in2 = '1' else '0';</li>

when in1='1' and in2='1' then out1 <= '1', otherwise out <= '0'</li>

• Concurrent 2) with-select-when: Signal based

## **Outline**

- Architectural Design Methods

- Data Flow Design (concurrent statements)

- Structural Design ("port map")

- Behavioral Design ("process")

- Concurrent vs. Sequential Statements

- Design Constructions

- Concurrent: when-else, with-select-when

- Sequential: if-then-else, case-when, loop

# Sequential 1) if-then-else

```

in1

if (cond) then

out1

in2

statement;

end if;

entity if ex is

port(in1, in2: in std logic;

if (cond) then

out1: out std logic);

statement1;

end if ex;

else

statement2;

architecture if ex arch of if ex is

end if;

begin

process (b)

if (cond1) then

begin

statement1;

if in1 = '1' and in2 = '1' then

elsif (cond2) then

out1 <= '1';

statement2;

else

elsif ...

out1 <= '0';

else

end if;

statementn;

end process;

end if;

end if ex arch;

```

# Sequential 2) case-when

```

entity test case is

port (in1, in2: in std logic;

out1, out2: out std logic);

end test case;

architecture case arch of test case is

signal b: std logic vector (1 downto 0);

begin

00"|"11" means case "00" or "11"

process (b)

begin

... "=>" means "implies" not "bigger"

case b is

when "00" | "11"

⇒ out1 <= '0';

out2 <= '1';

when others

>> out1 <= '1';

out2 <= '0';

end case;

All cases must be present:

end process;

Use others to complete all cases

b <= in1 & in2;

end case arch;

```

Student ID: \_\_\_\_\_ Date: Name: \_\_\_\_

```

1 entity test case is

port (in1, in2: in std logic;

out1, out2: out std logic);

4 end test case;

5 architecture case arch of test case is

6 signal b: std logic vector (1 downto 0);

begin

8

process (b)

begin

10

case b is

11

when "00" | "11" => out1 <= '0';

12

out2 <= '1';

13

when others => out1 <= '1';

out2 <= '0';

14

15

end case;

16 end process;

b <= in1 & in2;

17

```

List line numbers of concurrent statements:

Answer:

Fill in the truth table:

| _ |      |      |      |      |  |

|---|------|------|------|------|--|

|   | b(1) | b(0) | out1 | out2 |  |

|   | 0    | 0    |      |      |  |

|   | 0    | 1    |      |      |  |

|   | 1    | 0    |      |      |  |

|   | 1    | 1    |      |      |  |

18 end case arch;

# Concurrent vs. Sequential Constructions

#### Concurrent

#### when-else

#### $b \leftarrow "1000" \text{ when } a = "00" \text{ else}$

"0100" when a = "01" else

"0010" when a = "10" else

"0001" when a = "11";

#### with-select-when

#### with a select

b <= "1000" when "00",

"0100" when "01",

"0010" when "10",

"0001" when "11";

#### **Sequential**

#### if-then-else

if a = "00" then b <= "1000"

elsif **a = "01"** then **b <= "1000"**

elsif **a = "10"** then **b <= "1000"**

else b <= "1000"

end if;

## case-when

#### case a is

when "00"  $\Rightarrow$  b  $\Leftarrow$  "1000"; when "01"  $\Rightarrow$  b  $\Leftarrow$  "0100";

when "10" => b <= "0010";

when others => b <= "0001";

# **Sequential 3) 100p (1/2)**

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity for_ex is

port (in1: in std_logic_vector(3 downto 0);

out1: out std_logic_vector(3 downto 0));

end for_ex;

architecture for_ex_arch of for_ex is

begin

```

```

process (in1) while-loop

variable i: integer := 0;

begin

while i < 3 loop

out1(i) <= not in1(i);

end loop;

end process;</pre>

```

end for\_ex\_arch;

# **Sequential 3) 100p (2/2)**

for-loop

```

for <u>i</u> in 0 to 3 loop

out1(i) <= not in1(i);

end loop;</pre>

```

- The <u>loop parameter</u> (e.g.,

i) does NOT need to be declared.

- It is implicitly declared within the loop.

- It may not be modified within the loop (e.g., i := i-1;).

- for-loop is supported for synthesis.

while-loop

```

variable i: integer:=0;

...

while i < 3 loop

out1(i) <= not in1(i);

end loop;</pre>

```

- The while loop repeats if the condition tested is true.

- The condition is tested before each iteration.

- while-loop is supported

by some logic synthesis

tools, with certain

restrictions.

https://www.ics.uci.edu/~jmoorkan/vhdlref/for\_loop.html https://www.ics.uci.edu/~jmoorkan/vhdlref/while.html

Student ID: \_\_\_\_\_ Date: Name:

Rewrite arch1 without a process()

```

architecture arch1 of ex1

is

is

begin

begin

process (in1)

begin

for i in 0 to 3 loop

out1(i) <= not in1(i);

end loop;

end process;

end for ex arch;

end for ex arch;

```

architecture arch1 of ex1

# **Summary**

- Architectural Design Methods

- Data Flow Design (concurrent statements)

- Structural Design ("port map")

- Behavioral Design ("process")

- Concurrent vs. Sequential Statements

- Design Constructions

- Concurrent: when-else, with-select-when

- Sequential: if-then-else, case-when, loop